Note: Currently it’s only tested for Virtex-6 XC6VLX240T, suppose to be able to extend for more virtext-6 FPGAs

Work Environment

- Windows 7 64bit

- Xilinx Virtex-6 FPGA ML605 Evaluation Kit

Installation Guide

- Unzip the OpenOCD binary zip file to anywhere you’re used to put a tool, like

d:\tools\ Add the OpenOCD executable path to the

PATHenvironment, reboot or logout to put it into effectNote: if you’re using

cmder, we can make it without a rebooting- Go to Setting->Startup->Environment

- Set the

PATHenvironment:set PATH=D:\tools\openocd\bin;%PATH% - Open a new console to load the new environments

Install USB JTAG cable driver

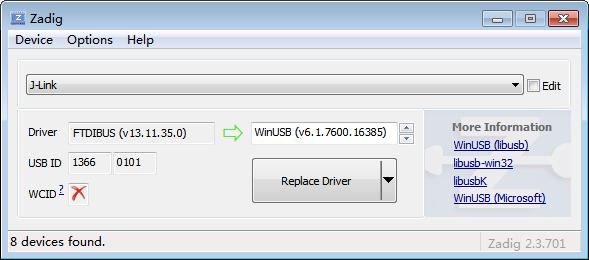

The adapter DLC9G that comes with Xilinx Virtex-6 Evaluation Kit is not supported by OpenOCD due to its proprietary protocol, here we’ll use jlink instead.- Download zadig

- Go to Options->List All devices

- Select the jlink device, vid: 1366, pid: 0101

Click “Replace Driver”.

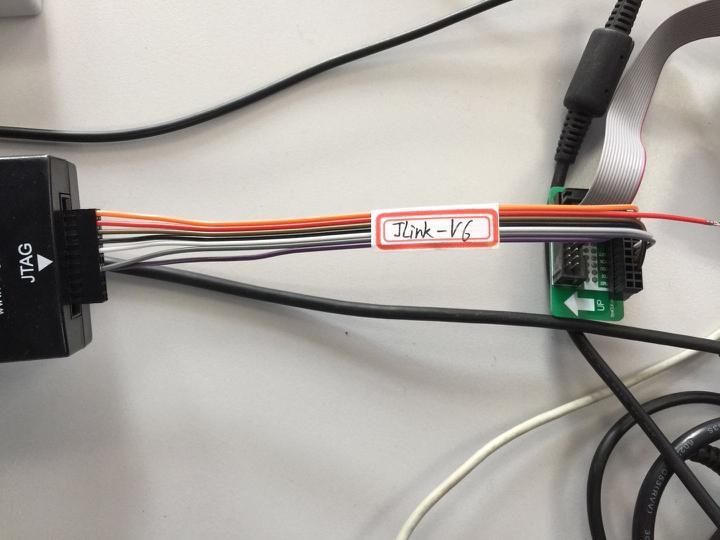

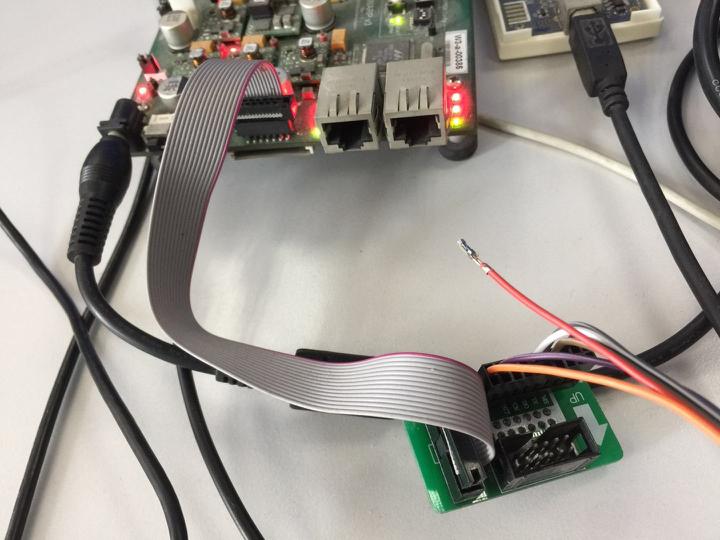

Jumper wiring jlink pins to jtags pins on board

Programming

Put the OpenOCD configuration file in the work dir together with the bit file (file content attached at the end).

1

2

3

4

5cd d:\workdir

dir

openocd-xc6v.cfg

xilinx-xc6v.cfg

bitstream.bitModify the path to the bit file in the configuration

1

2

3

4

5

6...

init

xc6v_program xc6v.tap

pld load 0 bitstream.bit #### this one ####

exit

...Run openocd in the cmd.exe or a cmder console

1

$ openocd -f interface/jlink.cfg -f xilinx-xc6v.cfg -f openocd-xc6v.cfg

Waiting for the programming done if no error raised

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15$ openocd -f interface/jlink.cfg -f xilinx-xc6v.cfg -f openocd-xc6v.cfg

GNU MCU Eclipse 64-bits Open On-Chip Debugger 0.10.0+dev-00404-g20463c28 (2018-01-23-12:30)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'.

xc6_program_iprog

adapter speed: 5000 kHz

Info : J-Link ARM V8 compiled May 27 2009 17:31:22

Info : Hardware version: 8.00

Info : VTarget = 2.478 V

Info : clock speed 5000 kHz

Info : JTAG tap: xc6.tap tap/device found: 0x84250093 (mfg: 0x049 (Xilinx), part: 0x4250, ver: 0x8)

Warn : gdb services need one or more targets defined

loaded file bitstream.bit to pld device 0 in 46s 322000us

OpenOCD Configuration (openocd-xc6v.cfg)

1 | adapter_khz 5000 |

OpenOCD Target Configuration (xilinx-xc6v.cfg)

1 | if { [info exists CHIPNAME] } { |